### Neptun - ECC Processor for RFID Tags and Smart Cards

Erich Wenger wengere@student.ethz.ch erich.wenger@student.tugraz.at

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

Integrated Systems Laboratory Swiss Federal Institute of Technology Gloriastrasse 35 CH-8092 Zürich, Switzerland

Institute for Applied Information Processing and Communications (IAIK) Graz University of Technology Inffeldgasse 16a 8010 Graz, Austria

Master Thesis

Supervisor: Dr. Norbert Felber, ETH Zürich Dr. Martin Feldhofer, TU Graz Assessor: Dr. Karl-Christian Posch, TU Graz

May, 2010

I declare that I have authored this thesis independently, that I have not used other than the declared sources / resources, and that I have explicitly marked all material which has been quoted either literally or by content from the used sources.

### Erich Wenger

| Signaturwert                 | SOAWpfA/+B+Vwu9PU0FjZJwgp0br1Cj7F67zRpOkOZKjBMFOa9L+b4bRS+jbgqyQGjLx0w |                                                                                                                             |  |

|------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

|                              | Unterzeichner                                                          | Erich Wenger                                                                                                                |  |

| DCERTIFICATE                 | Datum/Zeit-UTC                                                         | 2010-07-21T12:11:22Z                                                                                                        |  |

| SUND CERTIFICATE INFORMATION | Aussteller-Zertifikat                                                  | CN=a-sign-Premium-Sig-02,0U=a-sign-Premium-Sig-02,0=A-Trust Ges. f.<br>Sicherheitssysteme im elektr. Datenverkehr GmbH,C=AT |  |

|                              | Serien-Nr.                                                             | 467591                                                                                                                      |  |

|                              | Methode                                                                | urn:pdfsigfilter:bka.gv.at:binaer:v1.1.0                                                                                    |  |

|                              | Parameter                                                              | etsi-moc-1.1@69ec82f2                                                                                                       |  |

| Prüfinformation              | Prüfservice: https://www.signaturpruefung.gv.at                        |                                                                                                                             |  |

### Acknowledgements

First I would like to thank Martin Feldhofer from Graz University of Technology. He was the first contact for all cryptography-related questions. I am looking forward to working with him in the future.

Secondly I would like to thank Norbert Felber and the whole Integrated Systems Laboratory team at the ETH in Zürich. They have been a great support for all my hardware-relevant questions. Thank you for patience and your insight to ASIC design. It was a great pleasure working with this well experienced team. Especially Norbert Felber's constructive criticism was very helpful and highly appreciated. His experience helped me greatly.

Finally I would like to thank my girlfriend and my family for their unwaivering support and understanding over the last years.

### Abstract

Radio frequency identification (RFID) tags and smart cards already exist for years. These technologies are used for many different applications. Today, they are on the brink of conversion. The goal is it to combine the advantages of both technologies. The new generation of secure RFID tags should still be cheap and passively powered by an electromagnetic field (which is also used for communication with a reader), but they should also be capable of strong cryptographic algorithms.

The impact of such a product will be huge. Bar-codes will be replaced. Product piracy could be completely stopped using cloning-resistant RFID tags.

In order to achieve that goals, elliptic curve cryptography is used. The elliptic curve digital signature algorithm (ECDSA) requires small keys that result in a very small memory requirement. This makes ECDSA the best suited public-key authentication scheme currently known.

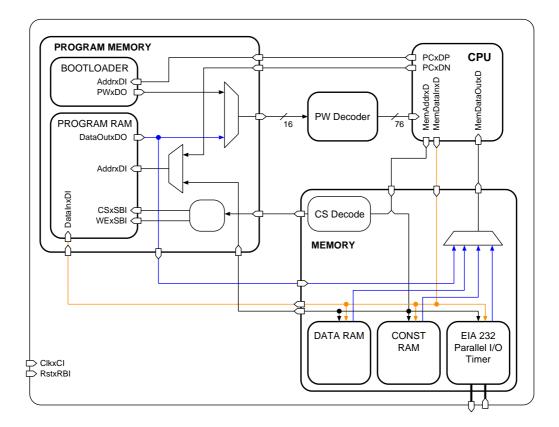

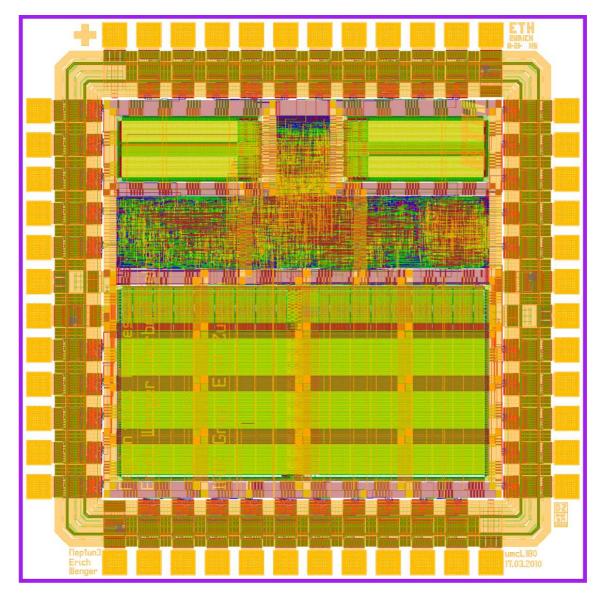

This work presents two different designs. One design called *Neptun* is a full-custom, embedded processor that can be used to evaluate different algorithms and security measures. This is especially important because the complex algorithms can be vulnerable to simple and differential power analysis attacks. *Neptun* is a programmable processor with an custom instruction set that was specially optimized for prime fields. The design also provides a bootloader, an EIA-232 interface, three timers and a parallel I/O. It has been implemented and fabricated as an application-specific integrated circuit (ASIC) using the UMC-L180 technology.

The elliptic curve digital signature generation and verification algorithms have been implemented using a custom built processor simulator. This simulator is capable of parsing assembler source code and generating executables.

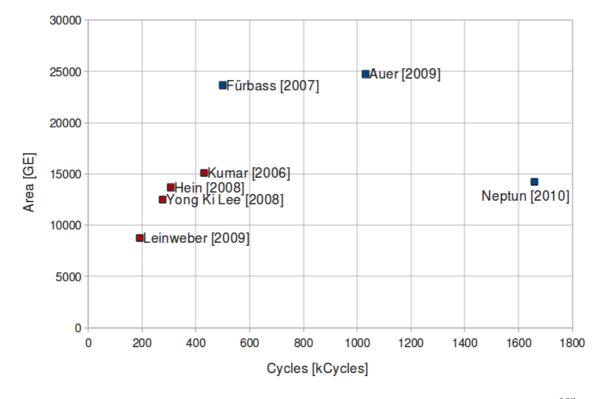

The second design is based on *Neptun*. The main difference is that it has been stripped from any unnecessary logic, but no compromise has been made concerning the security of the algorithms. This design is used to show that the presented architecture is viable for RFID tags. With the small area usage of only 14230 gate equivalents and a runtime of 1.65 million cycles, the design is competitive with designated co-processors and the smallest implementation for generating an ECDSA signature for NIST P-192, published so far.

With these results a big step to secure RFID tags has been done.

**Keywords:** Processor, Radio Frequency Identification, Elliptic Curve Cryptography, Digital Signature, ASIC

### Kurzfassung

Radio-Frequenz-Identifikations (RFID) Tags und Chipkarten existieren bereits seit Jahren. Diese Technologien werden für viele verschiedene Anwendungen genutzt. Heute haben sie den Punkt der Zusammenführung erreicht. Das Ziel ist es die Vorteile beider Technologien zu kombinieren. Die neue Generation von sicheren RFID-Tags soll billig und über ein elektromagnetisches Feld versorgt sein (dieses Feld wird auch zur Kommunikation mit einem Lesegerät benutzt). Aber sie sollen auch fähig sein, starke kryptografische Algorithmen zu berechnen.

Die Auswirkungen eines solchen Produkts werden immens sein. Barkodes werden ausgetauscht. Produktpiraterie könnte komplett gestoppt werden durch die Benutzung von kopierresistenten RFID Tags.

Um diese Ziele zu erreichen, wird Elliptische-Kurven Kryptografie verwendet. Der Elliptic Curve Digital Signature Algorithm (ECDSA) verwendet kurze Schlüssellängen. Dies bewirkt eine geringe Speicheranforderung. Damit ist ECDSA das am besten geeignete asymmetrische Authentifizierungsverfahren.

Diese Arbeit präsentiert zwei Designs. Ein Design, mit dem Namen Neptun ist ein maßgeschneiderter, eingebetteter Prozessor, der zur Evaluierung verschiedener Algorithmen und Sicherheitsmaßnahmen verwendet werden kann. Dies ist besonders wichtig da die komplexen Algorithmen anfällig für simple und differentielle Leisungsanalyseattacken sind. Neptun ist ein programmierbarer Prozessor mit einem maßgeschneiderten Instruction-Set, das speziell für Primfelder optimiert wurde. Das Design beinhaltet auch einen Bootloader, eine EIA-232 Schnittstelle, drei Timer und eine parallele I/O-Einheit. Es wurde implementiert und hergestellt als ein applikationsspezifischer integrierter Schaltkreis (ASIC) unter der Verwendung der UMC-L180 Technologie.

Die Elliptischen Kurven Signatur-Erzeugung und Verifikations-Algorithmen wurden unter Verwendung eines maßgeschneiderten Prozessor-Simulators implementiert. Dieser Simulator ist auch fähig Assembler-Kode zu analysieren und ausführbare Dateien zu erzeugen.

Das zweite Design basiert auf *Neptun*. Der größte Unterschied ist, dass es von jeglicher unnötigen Logik befreit wurde, ohne einen Kompromiss bei der Sicherheit der Algorithmen einzugehen. Dieses Design wird dazu benutzt, dass die aufgezeigte Architektur praktikabel für RFID-Tags ist. Mit einem geringen Platzverbrauch von nur 14230 Gatteräquivalenten und einer Laufzeit von 1,65 Millionen Zyklen ist das Design vergleichbar mit dedizierten Koprozessoren und die kleinste Implementierung zur Erzeugung von ECDSA-Signaturen (unter der Verwendung der NIST P-192 Parameter), die bis jetzt publiziert wurde.

Mit diesen Resultaten wurde ein großer Schritt zu sicheren RFID-Tags gemacht.

Stichwörter: Prozessor, Radio-Frequenz-Identifikation, Elliptische-Kurven Kryptografie, Digitale Signatur, ASIC

### Contents

| 1        | <b>Intr</b><br>1.1             | oduction       1         Outline       2                           |  |  |  |  |

|----------|--------------------------------|--------------------------------------------------------------------|--|--|--|--|

| 2        | <b>Intr</b><br>2.1             | Production to Chip Cards3Applications42.1.1 Wireless Applications5 |  |  |  |  |

| 3        | An                             | Introduction to Cryptography 7                                     |  |  |  |  |

|          | 3.1                            | Definition and Goals                                               |  |  |  |  |

|          | 3.2                            | Symmetric-Key Cryptography                                         |  |  |  |  |

|          |                                | 3.2.1 Key-Distribution System                                      |  |  |  |  |

|          | 3.3                            | Public-Key Cryptography 10                                         |  |  |  |  |

|          | 3.4                            | Comparison of Cryptography Schemes                                 |  |  |  |  |

|          | 3.5                            | Digital Signatures 11                                              |  |  |  |  |

|          | 3.6                            | Hash Functions                                                     |  |  |  |  |

| 4        | Dig                            | ital Signature Algorithms 13                                       |  |  |  |  |

|          | 4.1                            | Digital Signature Algorithm                                        |  |  |  |  |

|          | 4.2                            | Elliptic Curve Digital Signature Algorithm 14                      |  |  |  |  |

|          |                                | 4.2.1 Signature Generation                                         |  |  |  |  |

|          |                                | 4.2.2 Signature Verification                                       |  |  |  |  |

| <b>5</b> | Elliptic Curve Cryptography 18 |                                                                    |  |  |  |  |

|          | 5.1                            | Mathematical Basics                                                |  |  |  |  |

|          | 5.2                            | Adding and Doubling 21                                             |  |  |  |  |

|          | 5.3                            | Point Multiplication                                               |  |  |  |  |

|          | 5.4                            | Comparison of Point Multiplication Algorithms                      |  |  |  |  |

| 6        | Prii                           | ne Field Arithmetic 27                                             |  |  |  |  |

|          | 6.1                            | Addition and Subtraction                                           |  |  |  |  |

|          | 6.2                            | Integer Multiplication                                             |  |  |  |  |

|          | 6.3                            | Reduction                                                          |  |  |  |  |

|          |                                | 6.3.1 NIST-P192                                                    |  |  |  |  |

|          |                                | 6.3.2 NIST-P256                                                    |  |  |  |  |

|          | 6.4                            | Montgomery Multiplication                                          |  |  |  |  |

| <b>7</b>     | Des            | ign Flow for Processor Creation 3-    | 4        |

|--------------|----------------|---------------------------------------|----------|

|              | 7.1            | Features of the Simulated Processor   | 4        |

|              |                | 7.1.1 Data Structure                  | 5        |

|              |                | 7.1.2 Virtual Processor               | 7        |

|              | 7.2            | Implementation of the Algorithms      | 8        |

|              | 7.3            | Parallelizing the Commands            | 9        |

|              | 7.4            | Generating a Finite Instruction Set   | 0        |

|              |                | 7.4.1 Neptun Instruction Set          |          |

|              |                |                                       | -        |

| 8            | Eva            | luation of Platform 44                | 4        |

|              | 8.1            | Size Approximation                    | 4        |

|              | 8.2            | Runtime Analysis                      | 5        |

|              | 8.3            | Design Decision                       | 6        |

|              |                | 0                                     |          |

| 9            | $\mathbf{Pro}$ | cessor 4'                             | 7        |

|              | 9.1            | Architecture                          | 7        |

|              | 9.2            | CPU                                   | 8        |

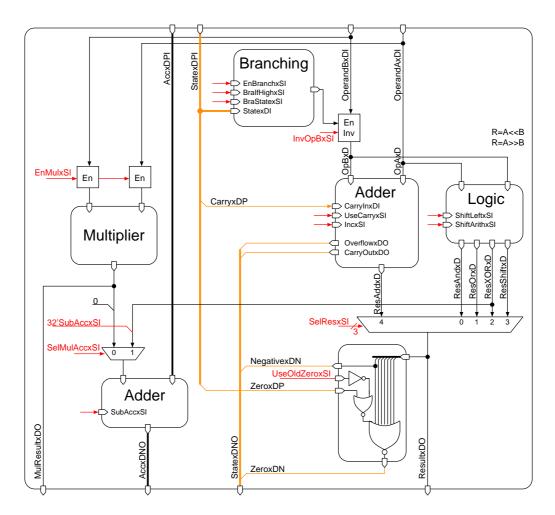

|              | 9.3            | ALU                                   | 1        |

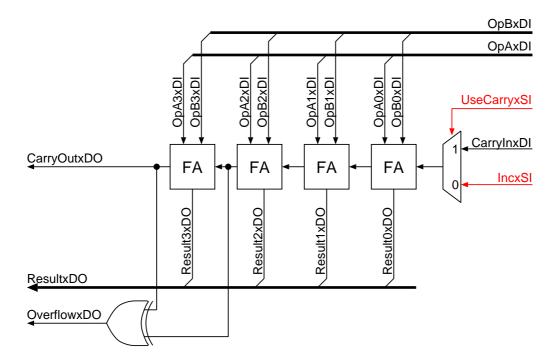

|              |                | 9.3.1 Adder                           | 1        |

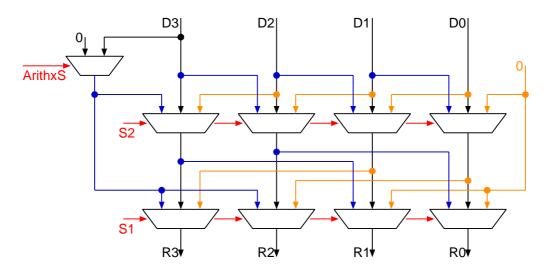

|              |                | 9.3.2 Barrel Shifter                  | 3        |

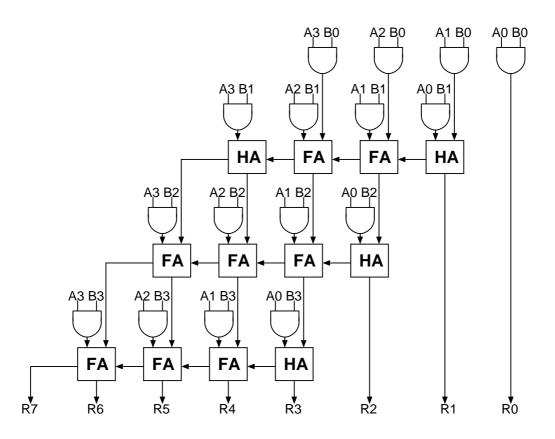

|              |                | 9.3.3 Multiply Accumulate             |          |

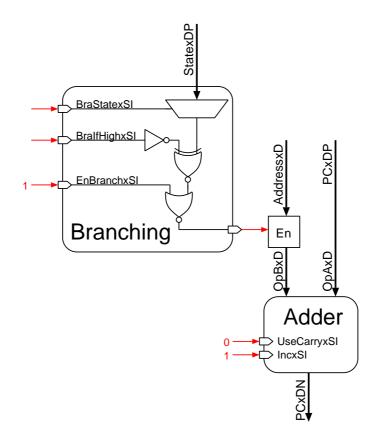

|              |                | 9.3.4 Branching                       |          |

|              | 9.4            | Reusable Processor Design             |          |

|              | 0.1            | 9.4.1 Instruction Set                 |          |

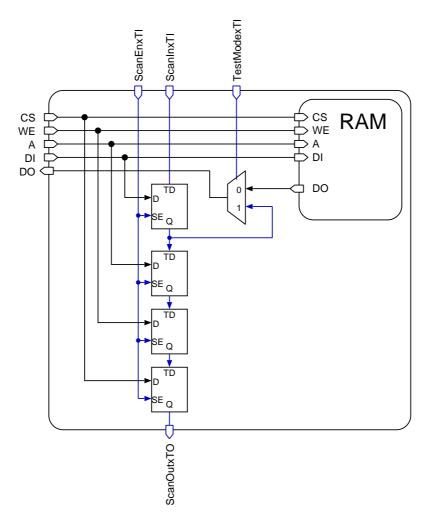

|              |                | 9.4.2 Test Strategy                   |          |

|              |                | 9.4.3 Bootloader                      | -        |

|              |                | 9.4.4 I/O Interfaces                  |          |

|              |                | 9.4.4 1/O Interfaces                  | 0        |

| 10           | $\mathbf{Res}$ | ults 65                               | <b>2</b> |

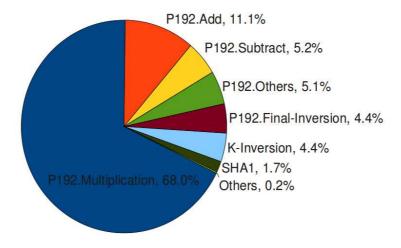

|              |                | Algorithm Analysis                    |          |

|              | 1011           | 10.1.1 Signature Generation           |          |

|              |                | 10.1.2 Signature Verification         |          |

|              | 10.2           | Area Analysis of Neptun   6           |          |

|              |                | Area Analysis of Low-Area Designs   6 |          |

|              | 10.0           | 10.3.1 Program Memory Implementation  |          |

|              | 10.4           | Possible Improvement                  |          |

|              |                | Comparison with other Work            |          |

|              | 10.0           |                                       | 2        |

| 11           | Cor            | aclusions 74                          | 4        |

|              | 001            |                                       |          |

| $\mathbf{A}$ | Abb            | previations 7                         | 7        |

| P            | Pro            | cessor 77                             | 8        |

| Б            | B.1            |                                       |          |

|              | 2.1            |                                       |          |

|              | D.2            | Pin Configuration                     |          |

|              | Ъa             | B.2.1 Pin Description                 |          |

|              | B.3            | Memory Mapping                        |          |

|              | B.4            | Bootloader                            |          |

|              |                | B.4.1 SPI Flash                       | 1        |

|              | B.4.2 Serial Interface             | 81 |

|--------------|------------------------------------|----|

| С            | I/O Interfaces         C.1 EIA-232 | 85 |

| D            | Montgomery Ladder Implementation   | 87 |

| $\mathbf{E}$ | Original Assignment                | 89 |

| Bi           | bliography                         | 90 |

## Chapter 1

### Introduction

The importance of devices that use a combination of radio frequency identification (RFID) and security technology has grown over the last few years. Several products with security features already exist nowadays. Several of them have already been broken (MIFARE Classic, Keeloq). Their security was mainly based on using custom and secret algorithms. Secure systems should be based on openly available algorithms. Only the key(s) should be kept secret.

The concept behind RFID is that a very small microchip is attached to an antenna. The chip is powered via an electromagnetic field of the reader. The field is also used to communicate with the RFID chip. Because the energy is transferred over a distance, the power consumption for an RFID tag is critical.

Unlike RFID tags, smart cards are systems that use strong cryptographic algorithms. To process those complex algorithms, usually powerful processors are used as smart cards. The power for such cards is usually provided by an active power supply via a galvanic connection. So it has not been very important to keep the power consumption of such cards low.

During the last few years, wireless interfaces have been added to the smart cards. Because of the relatively huge power consumption of smart cards the possible range for that systems is in the area of centimeters.

The idea is to merge the RFID and smart card technologies. The price and range of the new product should be similar to RFID tags, but the security of this product should be as strong as the security of a smart card. To achieve those goals, several restrictions need to be made. One is to highly optimize the intended target tag for a certain kind of security method.

Investigations showed that elliptic curve cryptography is well suited for such applications. It is very resource conservative and based on difficult mathematical problems. The elliptic curve digital signature algorithm is a well established concept for authentication. To be compatible to commonly used standards, standardized NIST curves are used in this design. The set of used domain parameters is called NIST P-192. The advantage of the used prime field is that very fast reductions are possible. As a result, a reasonably low total runtime is achievable.

This thesis presents two different designs. One design, called *Neptun* makes use of a custom build processor and can be used to evaluate different algorithms and security measures. The problem with full-custom ASIC designs is that errors are very expensive. Especially simple and differential power analysis attacks can be used to attack security devices. So the used algorithms need to be carefully evaluated and possible security flaws need to be fixed. The second design is based on *Neptun*. The main difference is that it is optimized for one cryptographic algorithm. This design is used to show that the presented concept can be used as an area optimized design. The used silicon area usually is proportional to the prices of a chip. Because RFID tags are usually intended to be bulk commodity, the low area requirement is especially important.

The possible applications for such a presented design are immense. It can be used in every environment, where authentication and access control is important. An example are the huge losses in the range of billions that are caused by counterfeit products. Securityenabled RFID tags can be used to identify counterfeit products. This method has the potential to reduce product piracy.

#### 1.1 Outline

This thesis will start with an introduction to smart cards. Chapter 2 gives a short history of chip cards. Especially the applications are important. The presented chip can be used by all of them.

Subsequently this thesis can be split into three parts. The cryptographic algorithms, the hardware for the specialized processor and the discussion of results. Chapter 3 handles an introduction to cryptography. Very general topics like definitions and goals of cryptography as well as symmetric- and public-key cryptography are covered. Naturally those two cryptographic schemes are compared.

Chapter 4 handles digital signatures. The older digital signature algorithm is shortly discussed for comparison with the elliptic curve digital signature algorithm. Both, the signature generation and the signature verification process are discussed in detail. Also the correctness of ECDSA is shown.

To actually understand ECDSA, elliptic curve arithmetic is introduced in Chapter 5. This chapter describes the basic concepts behind elliptic curves as well as point arithmetic. The focus is especially on the performance-relevant point multiplication schemes.

Elliptic curves make use of finite fields. Chapter 6 introduces techniques that are needed to handle prime-field arithmetic on platforms with small data paths. The focus is especially on the multiplication and reduction methods.

Chapter 7 is used as transition from the used algorithms to the ASIC hardware. It describes how a design can be developed, optimized and simulated. Different instructionset concepts are discussed. Those instruction sets are described in connection with the design flow used for the *Neptun* processor.

By having the idea of a certain design in mind, different designs are discussed in Chapter 8. Size as well as runtime approximations are made.

With the decided design in the back of the mind, a processor is designed in Chapter 9. After the discussion of a general architecture concept and a central processing unit, an arithmetic-logic unit and all its components are described. With some modifications, the processor is made reusable. Also an efficient method for testing is described.

All the previous information has been used to implement a processor, called *Neptun*. Several attributes of this processor are discussed in Chapter 10. After a detailed runtime analysis, the area requirement is discussed and compared to different publicly known designs.

Finally, conclusions are given in Chapter 11. The appendix is used to document various features of the implemented processor in detail.

### Chapter 2

### **Introduction to Chip Cards**

Comprehensive material about chip cards can be find in the book [33]. Especially for this thesis relevant chapters are 1, 2, 12, 13 and 14 and are summarized at this place.

The popularity of plastic cards began in the beginning of the 50s in the USA. The cheap plastic PVC made the production of robust and durable cards possible. It was far superior to the cards made from paper or cardboard.

The first full plastic card for payments was offered by Diners Club in the year 1950. It was designated for an exclusive group of people. At first the acceptance of the card was limited to certain hotels and restaurants.

After Visa and MasterCard joined the scene the spread of the plastic money grew increasingly.

Nowadays, the plastic cards makes it possible to pay worldwide without cash money. The owner can pay every time and everywhere without the risk of stolen cash.

In the beginning, the used security measures were very simple. They were based on visual information like an embossed number, an owner and a signature field. This level of tamper resistance was not enough, once the popularity reached a certain point. A first improvement was to add a magnetic stripe on the back of the cards. This added machine-readable data to the cards. This feature reduced the required use of paper but had a flaw. The information on the magnetic stripe could be read, written and deleted by anybody who owned the right equipment. So the magnetic stripe cannot be used for the storage of secret information.

The development of integrated circuits in the 70s and 80s made it possible to integrate a lot of logic on a tiny chips. The big break through was made in 1984. The french PTT made a field trial for phone cards. The tested chip cards were very tamper proof and reliable. The tested chip cards also showed a big flexibility in its applications.

These cards were using simple circuits with security. So they were cheap for production. Also the more complex microprocessor chips were first tested in telecommunications. Because of the positive experience during the use of chip cards in the analog mobile telephone system, chip cards are used for authentication in the GSM network. This was setup in many European countries in 1991. Currently there are more then 600 million user in more than 170 countries.

The development of chip cards in the banking industry was slower. Mainly because the hardware and software for the required mathematical algorithms is very complex. With the introduction of modern cryptography, chip cards became more and more popular. The first country with a nationwide introduction of chip cards for payment was Austria. These chip cards were capable of POS (point of sales) functions, an electronic purse and possible

extensions.

Chip cards present a very important function: electronic signatures. The European parliament released a directive in the year 1999 for the legal foundation of digital signatures.

Apart from the galvanic coupled cards also wireless cards were introduced. Their handling is a lot simpler and more user-friendly. Also the possible fields of applications extended with their introduction.

### 2.1 Applications

- **Debit card.** This kind of cards makes it possible to pay at the shop directly. Using the debit card, a transaction is started from the owners bank account and the money is transferred to the dealer or service provider.

- **Electronic purse.** Using a terminal of some kind, money can be stored directly on the card. During payment, the balance of the card is decreased and the balance of the second party (usually the dealer) is increased.

This system is fairly complex. The properties are:

- Automatic process ability. In order to operate such systems profitably the transactions must be processable by machines.

- **Transferability.** The money should not be bound to a certain medium. It must be transferable via various networks of PCs.

- **Divisibility.** A certain amount of money must be splitable into several parts. This makes it possible to pay exactly the amount that should be paid.

- Non central. A transaction of money should be possible when both parties are offline and have no connection to a banking system. Debit or credit cards are usually managed by a central administration.

- Monitoring. This requirement is important. There are two cases to consider. In one case there is somebody attacking the system. In the other case there is an error in the system and it is malfuctioning. Both of those procedures must be monitorable or signal some kind of administrator.

- **Security.** The most basic requirement is the protection against forgery. The system would break down immediately if money can be copied or forged.

- Anonymity. This means that it should not be possible to map the payments between people. There are two positions to be considered: The operator wants a non-anonymous system, so he can monitor it optimally. The user wants complete anonymity and no traceability.

- **GSM.** The chip card for GSM (Global System for Mobile Communications) telephones is named SIM (subscriber identity module). It represents the identity of a party. Its primary function is to secure the authenticity of a mobile station in a network. Apart from that, a SIM also supports additional functions. It provides the secure execution of programs, the storage of data (phone numbers, short messages and personal adjustments for the mobile phone) and other mobile services.

The main task of the SIM is the authentication in the GSM network. This is a one-way authentication. The network checks the authenticity of the SIM but the SIM does not check the authenticity of the network. The identification of the SIM works with a, for GSM unique, 8-byte number called the IMSI (international mobile subscriber identity). With this number, the subscriber can be identified worldwide.

- **UMTS.** The Universal Mobile Telecommunication System (UMTS) is declared as the third generation of mobile telecommunication. From the view of the chip card, the biggest difference is the new security module: the USIM (universal subscriber identity module). It uses the ISO/IEC 7816 standards and is backwards compatible with the old norm (the SIM).

- **Health insurance card.** This card provides two basic functions: On the one hand it is an authentication of the patient to the doctor. It can be seen as an electronic health insurance certificate. On the other hand it is a data storage for the computer of the doctor. It can contain billing information and/or a patient history.

- **Digital signature.** A legally binding signature requires two prerequisites: A law that binds all participants legally and a powerful chip card. The card must be capable of numeric operations and the storage of a private key. For that a powerful processor or co-processor is required.

#### 2.1.1 Wireless Applications

There are two kinds of cards that need to be distinct. Although the requirements and the applications for those cards are merging.

The first kind are wireless smart cards. Traditionally smart cards have very powerful embedded processors. These processors are mostly used for various different cryptographic algorithms. Some applications are already mentioned in the previous section. Because these embedded systems are so powerful they usually require a lot of power (in the range of milliwatts). The wireless interface used for those cards is the ISO-14443. Typically the operation range of such a card is some centimeters.

Another type of cards are RFID (Radio Frequency Identification) cards. They are designed to have a wider range of up to several meters. To achieve such distances, the power consumption of such cards must be very low (in terms of microwatts). So the implementations of RFID cards were very limited. Usually they were used to store several bytes of data. Later, some manufacturers implemented symmetric algorithms that can be used to encrypt the connection between a tag and a reader. Many of those algorithms were broken during the last few years.

Other applications are:

- **Skiing.** The type of cryptography used for skiing traditionally is limited. It is more important for this application that the range of the used RFID cards is high. Security is achieved with different methods. Every card contains a unique serial number. All the readers within a skiing area are connected to a central server. At first the serial number is checked for its validity. Because the last position within the skiing area is logged a causality check can be performed. A user cannot be at two distinct places in the skiing area within several seconds. A third check is that pictures are taken of the skiers. The readers are equipped with web cams. So the operator can compare the stored image with the web cam.

- **Textile industry.** Nowadays barcodes are placed on every item sold in a store. The barcodes are unique for a type of product. So the barcode can be used at the

cashier for product identification. This information can be used for billing. A goal of the industry is to replace the barcodes by RFID tags. A product can be uniquely identified per item and per class. This should result in the following changes:

- RFID reader terminals can be placed at the entries of a stock. In this way the number of items is always up to date. This procedure simplifies the required stock management. Pallets of items can be scanned at once.

- RFID readers can be placed at exits of shops. Because every item can be identified uniquely, every item can be checked if it has been paid for. This provides a cheap way to prevent shop lifting. This ability causes problems. The tags can be destroyed or covered in aluminum foil. Then the security system does not work any more.

- The payment at the cashier can be accelerated. The cashier does not have to scan each item manually. A whole basket of products can be read at once. It does not even have to be emptied.

- In the textile industry, a lot of clothes and accessories are forged. A tag, sewed within the clothing can be used to check that it was produced by the declared trade mark. The tag can simply contain a digital signature that was issued by the manufacturer.

- Access control. This field of application is huge. It does not only cover the access control to certain areas of a nuclear reactor, secret agencies, office buildings... It also covers active tags used as car keys or remote controlled garage door opener. The currently existing tags are used in a lot of different systems. Usually the systems use some kind of authentication systems. The elliptic curve digital signature algorithm is well suited for the most of those applications (see Chapter 4).

### Chapter 3

### An Introduction to Cryptography

Cryptography already exists for thousands of years. One very popular and old cipher is the Cesar code. It is a very simple cipher. Every letter in a sentence is rotated by a number of positions. Modern cryptography is based on hard mathematical problems.

This chapter gives a short introduction to cryptography. Just enough to understand the basics behind elliptic curve cryptography, described in the next chapter. For more information about cryptography in general have a look in [30].

### **3.1** Definition and Goals

Based on [30], cryptography is defined as the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication and data origin authentication.

Let us look on this attributes in detail:

- **Confidentiality** stands for secrecy and privacy. This means that nobody, except the person authorized, should be able to access the unencrypted information.

- **Data integrity** is about the unauthorized change or alteration of data. It must be possible to detect manipulation of data by unauthorized parties. Manipulation can be the insertion, deletion or substitution of data.

- Authentication and identification go hand in hand. Two different forms of authentication can be distinguished: Entity authentication is about proving ones authenticity using certain information about oneself to a second party. Origin authentification proves that the provided data/message/information is from a certain sender.

- **Non-repudiation** prevents an entity from denying previous commitments or actions. In the case of a signed contract, this attribute makes sure that a party cannot back out, by denying that the contract was signed.

The goal of cryptography is it to handle those attributes adequate with the available algorithm(s). Every available algorithm should be evaluated. There are various criteria for such an evaluation:

Level of security is usually defined as the number of operations needed to attack the intended objective (e.g. encryption). Because the best method for 'cracking' an algorithm is often discovered over time, the level of security degrades over time.

Most often, the available computational resources for cracking an algorithm are important as well.

- **Functionality.** [30] describes it as the primitives needed to be combined to meet various information security objectives. The most effective primitives for a given objective are determined by the basic properties of the primitives.

- Methods of operation. A primitive can have different functionality. This mostly depends on its mode of operation or usage. It also depends on the applied inputs.

- **Performance** refers to the efficiency of the primitive. For an encryption algorithm, this is the number of cycles or the time it takes to finish the encryption.

- **Ease of implementation** refers to the difficulty of practically implementing a primitive. This can vary, depending on the available software or hardware environment.

The importance of those criteria is dependent on the application and the used resources. As an example, let us look at the implemented ECDSA algorithm within this master thesis (using NIST-P192):

- Level of security is comparable to a 96-bit Triple-DES (Data Encryption Standard) or a 2048-bit RSA (Rivest-Shamir-Adleman) algorithm.

- **Functionality.** An input message can be signed using a private key. A public key can be used to verify this signature.

- Methods of operation. The algorithm can be used for signing a document (message) and for proofing ones authenticity.

- **Performance.** The performance is evaluated with two parameters: The area needed for implementing the algorithm in hardware and the number of cycles it takes to complete one ECDSA signature.

- **Ease of implementation.** In this case it is the time, needed for building the Neptun processor. Approximately five months.

### 3.2 Symmetric-Key Cryptography

In this cryptography scheme, both parties share the same secret key k, or one that can easily be derived from the other one. The plain message is m. The encoded message is c. An encryption function  $E_k$  is used to calculate  $c = E_k(m)$ . The decryption function  $D_k$ is used to derive the plain message from c:  $m = D_k(c)$ .

Previously, the Cesar cipher has been mentioned. In this case, the key is the number of positions that are shifted in the alphabet.

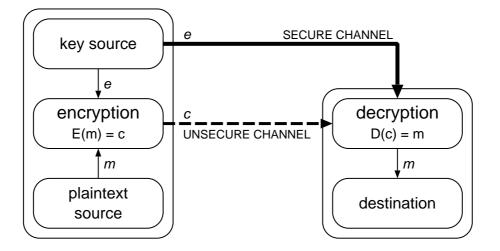

The biggest concern of a symmetric encryption scheme is to find a key that can be used by both parties. This problem is named as the key distribution problem. A secure channel is needed to exchange a secret key. Only then, symmetric-key encryption can be used (see Figure 3.1)

Symmetric-key encryption schemes can be split into two classes:

Figure 3.1: Encryption using symmetric cryptography.

- **Block ciphers** are encryption schemes that break a plain text message into blocks of fixed length. Every block is encrypted one by one. A very popular representative of block ciphers is the AES (Advanced Encryption Standard) algorithm. This is an algorithm invented by Joan Daemen and Vincent Rijmen (see [32]).

- **Stream ciphers** can be seen as block ciphers with a block length of one. This method does not need to collect data until a full block length is reached. Every character of the message can be encoded immediately. Famous examples of newly developed stream ciphers are Grain [14] and Trivium [6].

#### 3.2.1 Key-Distribution System

There are three methods for managing keys for symmetric algorithms:

- Store them all. Every entity stores a secret key used for communication with any other entity. To be prepared to communicate with (n-1) other entities, (n-1) keys are required. For an RFID tag this is intractable. In total  $n^2 n$  keys need to be stored in this system.

- **Trusted third party.** A third party is introduced. This party stores n keys for n participants. If two participants want to communicate, they first contact the third party using an encrypted connection. The third party generates a key that can be used by both parties. This key can be used for a secure connection between the two participants.

It is very interesting to review this approach for RFID tags. The third party is a central server. An RFID tag can encounter different readers and terminals during its lifetime. The first problem is a political problem because the readers are distributed throughout different companies. Secondly, all the readers must be online all the time, so that the tag can initialize a connection with the server. Thirdly, in the case of a server crash, all the keys can be lost, or the whole system does not work any more.

**Public-key cryptography.** Very often, the more calculation intensive, public-key cryptography is used for establishing a secure connection. A key exchange protocol is

used so that two parties can agree on a common key. This common key is then used for symmetric cryptography.

### 3.3 Public-Key Cryptography

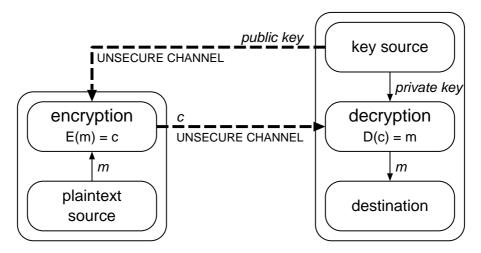

Public-key cryptography is also known as asymmetric cryptography. It is asymmetric because the two parties do not share their private key any more. Instead there is a public key, which can be used by any entity to encode a message  $c = E_{publickey}(m)$ . Encoding a message is a one-way trap function. Using the public key, the message m cannot be recovered. To decode the message, the private key is needed:  $m = D_{privatekey}(c)$ . This means that the private key is only known to the recipient of the encrypted message c. This scheme is visualized in Figure 3.2.

Figure 3.2: Encryption using public-key cryptography.

Note the difference between Figures 3.1 and 3.2. Using public-key cryptography, the public key can be transferred using an insecure channel. The channel for transporting the public key and the channel for the transportation of the message can also be the same.

A physical analog is a post box. Anybody can put something into the box (encrypt a message). Only the post officer with the key for the post box can open it (decrypt a message). The only flaw in this metaphor is that the post officer usually is not the recipient of the mail.

Usually the term private key is used in connection with public-key cryptography and the term secret key is used in the case of symmetric cryptography. That is because a secret needs to be shared by two parties, but a key, which is only known to oneself, is really private.

### 3.4 Comparison of Cryptography Schemes

At this point it is interesting to compare the two previously introduced schemes. Advantages of symmetric-key cryptography:

- 1. High performance implementations are possible.

- 2. Short key lengths.

- 3. Can be used as pseudo-random number generators.

- 4. Symmetric-key ciphers can be combined. This results in strong product ciphers.

Disadvantages of symmetric-key cryptography:

- 1. The key must remain secret within all participating parties.

- 2. A lot of key pairs need to be managed in large networks. Trusted third parties need to be used.

- 3. Cryptographic practice dictates that the key is changed frequently. If possible it should be even changed within communication sessions.

Advantages of public-key cryptography:

- 1. The private key must be kept secret by one entity only. (The authenticity of public keys must be guaranteed).

- 2. Only a functionally trusted third party is required. Functionally trusted means that the third party does not have to store any private keys. In many cases an online connection to a third party is not required at all times.

- 3. The key pair can remain unchanged for long periods of time (several sessions or years). This also depends on the mode of usage.

- 4. There are many efficient digital signature mechanisms. They mostly only require small public keys.

- 5. The total number of required key pairs in a large network is much smaller than in a symmetric-key scenario.

Disadvantages of public-key encryption:

- 1. In comparison to symmetric-key schemes, the public-key schemes are computationally much more intensive.

- 2. The required key size is larger compared to symmetric-key encryption methods.

Optimally one should use the advantages of both worlds. Use public-key cryptography for establishing a secure connection but use symmetric-key cryptography for transferring the data.

### 3.5 Digital Signatures

A fundamental component in cryptography are digital signatures. They are essential for authentication, authorization and non-repudiation. The purpose is to bind an entity to a piece of information. During the process of signing, some secret information held by the signing entity is used to generate a signature for some information.

A perfect application for public-key cryptography are digital signatures. Two processes need to be distinguished:

Signing procedure. The signer creates a signature s for a message m by computing  $s = S_{privatekey}(m)$ . This results in the pair (m, s).

Verification procedure. Usually the verifier is not the same entity as the signer. As a result, the verification (public) key has to be obtained first. Using this information  $u = V_{publickey}(m, s)$  can be calculated. The signature is accepted if u is true. Else the signature is rejected.

### 3.6 Hash Functions

The book [30] states that a hash function is a computationally efficient function mapping binary strings of arbitrary length to binary strings of some fixed length, called hash-values.

A hash value can be seen as a compact representation of an input string. During this compression, the number of bits (from input to hash) gets reduced. This means that it is theoretically possible to find two input strings that generate the same hash value. This is called a collision. Hash algorithms are designed in a way that it is hardly possible to find a collision. It should be also computationally infeasible to find an input x for a predefined hash-value y so that h(x) = y. This is called a pre-image attack.

As it will be seen later, hash algorithms are very important for digital signatures and data integrity checks. During a signature generation, not the whole message is signed but the hash value of the message. So finding a message with the same hash-value as the originally signed message should be computationally infeasible.

To check the validity of a signature the hash function must be publicly known.

### Chapter 4

### **Digital Signature Algorithms**

This chapter gives a very short introduction to the Digital Signature Algorithm (DSA). The information from this introduction is used for comparison with the Elliptic Curve Digital Signature Algorithm (ECDSA). This algorithm is described in detail. The information used for this chapter is taken from [12].

### 4.1 Digital Signature Algorithm

Back in 1991, the U.S. National Institute of Standards and Technology (NIST) proposed the Digital Signature Algorithm (DSA). It was declared by the U.S. Government as Federal Information Processing Standard (FIPS 186) and called Digital Signature Standard (DSS).

DSA is based on Rivest, Shamir and Adleman (RSA). The RSA signature scheme use the fact that  $m^{ed} \equiv m \pmod{n}$  for all integers m. A e, d and n must fulfill certain properties. RSA can also be used for generating and verifying signatures, but they have a serious flaw. A signature for a defined message always results in the same signature.

This flaw is taken care of in the DSA Algorithms 1 and 2. The signature algorithm introduces a random ephemeral key. This is a private one-time key. This key is used for the exponentiation that was introduced by Rivest, Shamir and Adleman. This exponentiation is followed by some computations in lines 3 to 5, which results in the signature (r, s).

Algorithm 1 DSA signature generationRequire: Domain parameters (p, q, g), private key x, message m.Ensure: Signature (r, s).1: Select  $k \in_R [1, q - 1]$ .2: Compute  $T = g^k \mod p$ .3: Compute  $r = T \mod q$ . If r = 0 then go to step 1.4: Compute h = H(m).5: Compute  $s = k^{-1}(h + xr) \mod q$ . If s = 0 then go to step 1.6: Return(r, s).

This signature is used for the verification in Algorithm 2. This algorithm uses the signature, the message, the public key and the domain parameters. It neither uses the private keys k nor x that are only needed for the signature generation. As a result, the signature can be verified by doing the (previously introduced) exponentiation in line 5.

#### Algorithm 2 DSA signature verification

**Require:** Domain parameters (p, q, g), public key y, message m, signature (r, s). Ensure: Acceptance or rejection of the signature.

- 1: Verify that r and s are integers in the interval [1, q 1]. If any verification fails then return ("Reject the signature").

- 2: Compute h = H(m).

- 3: Compute  $w = s^{-1} \mod q$ .

- 4: Compute  $u_1 = hw \mod q$  and  $u_2 = rw \mod q$ .

- 5: Compute  $T = g^{u_1} y^{u_2} \mod p$ .

- 6: Compute  $r' = T \mod q$ .

- 7: If r = r' then return("Accept the signature"); Else return("Reject the signature").

### 4.2 Elliptic Curve Digital Signature Algorithm

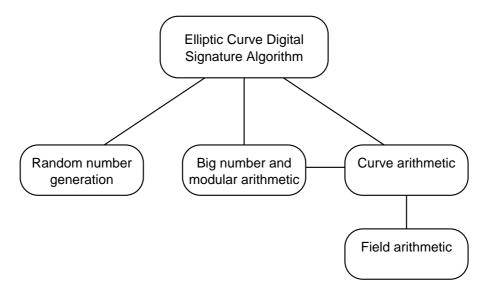

The Elliptic Curve Digital Signature Algorithm (ECDSA) is built on elliptic curve arithmetic, which is based on finite field arithmetic. Those dependencies are shown in Figure 4.1. In the case of this thesis, prime fields are used. So the 'field arithmetic' and the 'big number and modular arithmetic' blocks can be merged.

Figure 4.1: ECDSA uses curve arithmetic, which uses finite field arithmetic. Further a random number generator and modular arithmetic is required.

During the life cycle of a signature, several algorithms need to be performed.

- 1. Generate the domain parameters D. For that a domain parameter generation algorithm should be used (see Chapter 4.2 in [12]). In the case of this thesis, the parameters are already generated and part of the NIST standard FIPS 186-2 [31].

- 2. Generate a key pair (Q, d) using a key-generation algorithm. The algorithm used for Elliptic Curve Cryptography is shown in Algorithm 3. At first, it selects a random integer as private key. Then a point multiplication is performed with P. P is a previously selected domain parameter. The resulting point Q is used as public key.

- 3. A signature generation algorithm produces a signature, using the domain parameters D, an input message m and the private key d. It is shown in Algorithm 4.

- 4. At some point the signature needs to be verified. For that, Algorithm 5 is used. It uses the domain parameters D, the public key Q, the original message m and a signature (r, s). Very important is the fact that the verifier does not need the private key d for its verification. This signature is either accepted or rejected.

| Algorithm 3 Key-pair generation      |

|--------------------------------------|

| Require: Domain parameters           |

| Ensure: Public key Q, private key d. |

| 1: Select $d \in_R [1, n-1]$ .       |

| 2: Compute $Q = dP$ .                |

| 3: $\operatorname{Return}(Q, d)$ .   |

|                                      |

Before actually looking at the signature algorithm in detail it is necessary to understand the used parameters.

- p The order of the prime field  $\mathbb{F}_p$ . This is the underlying field used for all point additions, doublings and multiplications. It is a very important parameter because it greatly influences the performance of the point operations. Because the characteristic of p is neither 2, nor 3, a reduction of the Weierstrass equation can be performed. p is a domain parameter defined by NIST.

- a, b The coefficients of the elliptic curve  $y^2 = x^3 + ax + b$  satisfying  $rb^2 \equiv a^3(modp)$ . In the case of the NIST domain parameters those parameters are predefined. a = -3. 0 < b < p. Because a = -3 a field multiplication can be replaced by field additions.

- P = (x, y) The base point P is the starting point for each point multiplication, performed during the signature generation algorithm. It is represented with the two coordinates x, y. They are part of the NIST domain parameters. n The (prime) order of the base point P. Suppose  $Q = \infty$ . Now P is added to Q. Q = Q + P. This can be done n times, before the identity  $\infty$  is reached again. The parameter n is derived with the selection of P. So it is a NIST domain parameter.

- d, Q d is the private key. Q is the public key. They are generated using Algorithm 3. The public key Q is a point with two coordinates.

- r, s Those two parameters together represent a signature. Separately, they are useless.

There are additional parameters used for other underlying fields. This thesis uses prime fields. So only the for prime field important factors are considered.

#### 4.2.1 Signature Generation

A signature is generated using Algorithm 4. It is using the domain parameters, a private key and a message as inputs. k is selected randomly and used for a point multiplication. k is an ephemeral key. This is a private key that changes for each signature. From the resulting point, only the x-coordinate is needed. The conversion of  $x_1$  to  $\bar{x_1}$  is not needed if a prime field  $\mathbb{F}_p$  is used. In this case  $\bar{x_1} = x_1$  is valid. Because p > n, a reduction needs to be performed. In the following two lines, the second part s of the signature is calculated.

The major calculation is performed within line two. Usually the point multiplication takes more time to calculate than all the other operations together.

#### Algorithm 4 ECDSA signature generation

**Require:** Domain parameters, private key d, message m. **Ensure:** Signature (r, s). 1: Select  $k \in_R [1, n - 1]$ . 2: Compute  $kP = (x_1, y_1)$  and convert  $x_1$  to an integer  $\bar{x_1}$ . 3: Compute  $r = \bar{x_1} \mod n$ . If r = 0 then go to step 1. 4: Compute e = H(m). 5: Compute  $s = k^{-1}(e + dr) \mod n$ . If s = 0 then go to step 1. 6: Return(r, s).

It is interesting to compare the two presented signature Algorithms 1 and 4. A big difference are the used domain parameters and the different method for producing r. The second part of the signature generation algorithms, for generating s, is very similar.

#### 4.2.2 Signature Verification

To verify a given signature, Algorithm 5 is used. Apart from the signature itself, it needs the used domain parameters, the public key and the original message. After the calculation of  $u_1$  and  $u_2$ , two point multiplications need to be performed. Because of that, this algorithm uses up to twice the time compared to the signature generation algorithm.

Algorithm 5 ECDSA signature verification

**Require:** Domain parameters, public key Q, message m, signature (r, s).

**Ensure:** Acceptance or rejection of the signature.

- 1: Verify that r and s are integers in the interval [1, n 1]. If any verification fails then return ("Reject the signature").

- 2: Compute e = H(m).

- 3: Compute  $w = s^{-1} \mod n$ .

- 4: Compute  $u_1 = ew \mod n$  and  $u_2 = rw \mod n$ .

- 5: Compute  $X = u_1 P + u_2 Q$ .

- 6: If  $X = \infty$  then return("Reject the signature");

- 7: Convert the x-coordinate  $x_1$  of X to an integer  $\bar{x_1}$ ; compute  $v = \bar{x_1} \mod n$ .

- 8: If v = r then return("Accept the signature");

- Else return("Reject the signature").

In comparison with Algorithm 2 the first few lines are similar. Except for a different modulo,  $u_1$  and  $u_2$  are calculated identical.

It is very important to understand that the signature verification works without the private key. Let us assume for now that a signature (r, s) on a message m has been generated by a legitimate signer.

$$s \equiv k^{-1}(e + dr) \pmod{n}$$

$$k \equiv s^{-1}(e + dr)$$

$$\equiv s^{-1}e + s^{-1}rd$$

$$\equiv we + wrd$$

$$\equiv u_1 + u_2d \pmod{n}$$

Thus  $X = u_1P + u_2Q = (u_1 + u_2d)P = kP$ , and so v = r as required.

# Chapter 5 Elliptic Curve Cryptography

Elliptic curve arithmetic got popular in the 80's of the last century. That was the time when Neal Koblitz [24] was one of the first to use elliptic curves for cryptography. Since back then the popularity for elliptic curves grew more and more.

In the Austrian 'Bürgerkarte' and many other security-relevant environments, elliptic curves are used nowadays. The question is why they are doing so. The work [11] by Nils Gura et al. can provide an answer. They compared different RSA and elliptic curve algorithms on embedded processors. [12] states that a 224-bit elliptic curve and 2048bit RSA algorithm have the same level of security. Those two algorithms have been implemented by Nils Gura et al. on an 8-bit embedded processor (ATmega128). In detail, the secp224r1 curve (same as NIST P-224) is used for the elliptic curve arithmetic and the RSA-2048 algorithm is using the public exponent  $e = 2^{16} + 1$ . The resulting runtime of those algorithms has been within a 15%. The code size of both algorithms is also very similar (RSA is about 30% better). The big difference is in the required size of the data memory. The data memory of the RSA-2048 algorithm has to be more than three times larger than the memory of the 224-bit elliptic curve. This example clearly shows that the elliptic curve algorithms have a clear advantage for embedded devices, although the required algorithms are more complex.

Because the goal of this thesis is to lead the ECDSA algorithm one step closer to RFID devices, some basics are given in this section about elliptic curves. After a short introduction to elliptic curves, important double, add and multiplication algorithms are shown in this chapter.

### 5.1 Mathematical Basics

The equation behind each elliptic curve is a Weierstrass equation:

$$E: y^2 + a_1 x y + a_3 y = x^3 + a_2 x^2 + a_4 x + a_6$$

(5.1)

In order to ensure that the curve is 'smooth', there is also the discriminant  $\Delta \neq 0$  to consider.  $\Delta$  is the discriminant of E. It is defined with the following equation:

$$\Delta = -d_2^2 d_8 - 8d_4^3 - 27d_6^2 + 9d_2 d_4 d_6$$

$$d_2 = a_1^2 + 4a_2$$

$$d_4 = 2a_4 + a_1 a_3$$

$$d_6 = a_3^2 + 4a_6$$

$$d_8 = a_1^2 a_6 + 4a_2 a_6 - a_1 a_3 a_4 + a_2 a_3^2 - a_4^2$$

(5.3)

The smoothness of the elliptic curve is necessary, so that there are no points on the curve with two or more distinct tangent lines.

[12] states that E is defined over K because the coefficients  $a_1, a_2, a_3, a_4, a_6$  of its defining equation are elements of K. Sometimes E/K is written to emphasize that E is defined over K, and K is called the underlying field. Popular choices for those underlying fields are prime fields  $\mathbb{F}_p$  and binary extension fields  $\mathbb{F}_{2^m}$ . For both types of fields, parameters have been recommended by NIST in the FIPS 186-2 standard [31].

A point on the curve has the two coordinates x and y. This point is on the curve only if it satisfies the Weierstrass equation. This can be also written mathematically: L is an extension field of K. The set of L-rational points on E is defined as:

$$E(L) = \{(x,y) \in L \times L : y^2 + a_1 xy + a_3 y - x^3 - a_2 x^2 - a_4 x - a_6 = 0\} \cup \{\infty\}$$

(5.4)

$\infty$  is the point at infinity. This point can be seen as identity. It is important for the calculation with points.

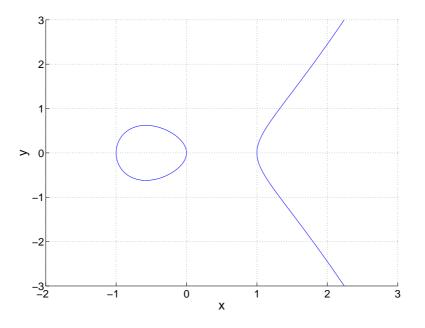

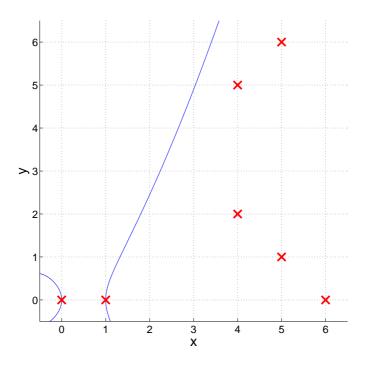

Figure 5.1: Elliptic curve represented over  $\mathbb{R}$ :  $E: y^2 = x^3 - x$ .

Figure 5.1 represents an elliptic curve. In this case E is defined over  $\mathbb{R}$ , or  $E/\mathbb{R}$ . The points that fulfill  $E(\mathbb{R}) \setminus \{\infty\}$  are drawn.

#### CHAPTER 5. ELLIPTIC CURVE CRYPTOGRAPHY

A very helpful construct is a transformation. A transformation is performed as an admissible change of variables. Such a transformation can be used to simplify the Weierstrass equation. It depends on some attributes of the underlying field K.

Dependent on the characteristic of K, the equation can be transformed differently. The possible simplifications can be done in the cases  $char(K) \neq 2, 3$ , char(K) = 2 or char(K) = 3. Because this thesis uses prime fields  $\mathbb{F}_p$  we can concentrate on  $char(K) \neq 2, 3$ . In this case, the following change of variables can be performed:

$$(x,y) \to \left(\frac{x - 3a_1^2 - 12a_2}{36}, \frac{y - 3a_1x}{216} - \frac{a_1^3 + 4a_1a_2 - 12a_3}{24}\right) \tag{5.5}$$

This transforms E to the curve:

$$y^2 = x^3 + ax + b (5.6)$$

a, b must be in K. The new discriminant can be written as  $\Delta = -16(4a^3 + 27b^2)$ .

It is helpful to recapitulate the information with an example. The characteristic of  $\mathbb{F}_7$  is neither 2, nor 3. The used equation is  $E: y^2 = x^3 - x$ . In this case  $a = 6 \equiv -1 \pmod{7}$  and b = 0. This is the same curve as in Figure 5.1. The resulting discriminant  $\Delta = -16(4a^3 + 27b^2) = -13824 \equiv 64 \equiv 1 \pmod{7} \neq 0$ . So the curve is valid and can be used. The resulting points on E are:

$$E(\mathbb{F}_7) = \{\infty, (0,0), (1,0), (4,2), (4,5), (5,1), (5,6), (6,0)\}$$

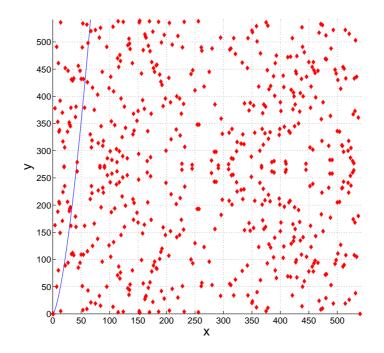

These points can be represented graphically. In Figure 5.2 the points on  $E: y^2 = x^3 - x$  are shown using  $\mathbb{F}_7$ . In Figure 5.3 the points on  $E: y^2 = x^3 - x$  are shown using  $\mathbb{F}_{541}$ .

Figure 5.2: Elliptic curve represented over  $\mathbb{F}_7$ :  $E: y^2 = x^3 - x$ .

Figure 5.3: Elliptic curve represented over  $\mathbb{F}_{541}$ :  $E: y^2 = x^3 - x$ .

### 5.2 Adding and Doubling

Adding two points can be done geometrically and with the use of formulas. At first, it is explained geometrically.

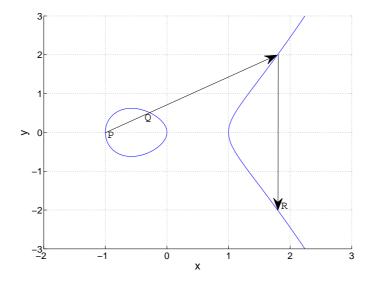

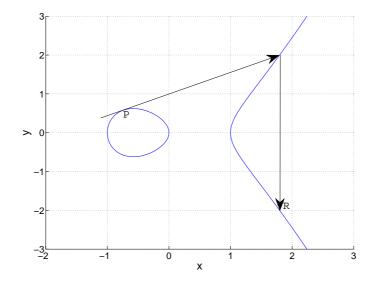

There are two points  $P = (x_1, y_1)$  and  $Q = (x_2, y_2)$  that should be added. Those two points are connected with a line. This straight line is extended until it intersects the elliptic curve at a third point. The point of intersection is mirrored along the x-axis. The resulting point  $R = (x_3, y_3)$  is the solution of the point addition. The addition is shown in Figure 5.4.

If the two points P and Q are equal, a doubling algorithm has to be applied instead. To double P, the tangent line at the point P needs to be found. This straight line is extended, until it intersects with the elliptic curve. The intersection is mirrored along the x-axis (similar to the addition). The resulting point is visualized in Figure 5.5.

To use points for calculation, several formulas need to be considered. This definition is taken from [12]. It is required that  $E \setminus K$ :  $y^2 = x^3 + ax + b$ ,  $char(K) \neq 2, 3$ :

**Identity.**  $P + \infty = \infty + P = P$  for all  $P \in E(K)$ .

**Negatives.** If  $P = (x, y) \in E(K)$ , then  $(x, y) + (x - y) = \infty$ . The point (x, -y) is denoted by -P and is called the *negative* of P; note that -P is indeed a point in E(K). Also,  $-\infty = \infty$ .

**Point addition.** Let  $P = (x_1, y_1) \in E(K)$  and  $Q = (x_2, y_2) \in E(K)$ , where  $P \neq \pm Q$ . Then  $P + Q = (x_3, y_3)$ , where  $x_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)^2 - x_1 - x_2$  and  $y_3 = \left(\frac{y_2 - y_1}{x_2 - x_1}\right)(x_1 - x_3) - y_1$ .

Figure 5.4: Graphical point addition. R = P + Q.

Figure 5.5: Graphical point doubling. R = 2P.

**Point doubling.** Let  $P = (x_1, y_1) \in E(K)$ , where  $P \neq -P$ . Then  $2P = (x_3, y_3)$ , where  $x_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)^2 - 2x_1$  and  $y_3 = \left(\frac{3x_1^2 + a}{2y_1}\right)(x_1 - x_3) - y_1$ .

### 5.3 Point Multiplication

The point addition and doubling formulas can now be used to derive a multiplication method. A simple multiplication method is displayed in Algorithm 6.

Unfortunately, this multiplication method is not safe from a Simple Power Analysis (SPA) attack. To the understand the problem of such an attack, a short excursion is

Algorithm 6 Right-to-left binary method for point multiplication Require:  $k = (k_{t-1}, ..., k_1, k_0)_2, P \in E(\mathbb{F}_q).$ Ensure: kP.1:  $Q \leftarrow \infty$ . 2: for *i* from 0 to t - 1 do 3: If  $k_i = 1$  then  $Q \leftarrow Q + P.$ 4:  $P \leftarrow 2P$ 5: end for 6: Return(Q).

necessary. Let us assume that there is a microprocessor that is used for the calculation of a point multiplication. Such a processor performs every part of the algorithm step by step (or line by line). Dependent on  $k_i$ , the processor will either add P to Q or not. This changes the runtime of a single loop cycle. This time can be measured. If  $k_i$  is one, the runtime is longer than in the case of  $k_i$  being zero. By measuring the power consumption during a point multiplication all bits of k can be recovered. This is a problem. Especially in the case that k is used as temporary private key (an ephemeral key) as it is in Algorithm 5. If k is discovered, the ECDSA signature generation algorithm is not secure any more.

So this vulnerability needs to be taken care of. Algorithm 7 shows a multiplication algorithm which is safe against SPA attacks. It is important to notice at this point that the algorithms is still vulnerable. Depending on the accessed addresses, the power trace changes minimally.

#### Algorithm 7 SPA safe point multiplication

**Require:**  $k = (k_{t-1}, ..., k_1, k_0)_2, k_{t-1} = 1, P \in E(\mathbb{F}_q).$  **Ensure:** kP. 1:  $Q[0] \leftarrow P$ . 2:  $Q[1] \leftarrow 2P$ . 3: **for** *i* from t - 2 to 0 **do** 4:  $Q[1 \oplus k_i] \leftarrow Q[k_i] + Q[1 \oplus k_i]$ 5:  $Q[k_i] \leftarrow 2Q[k_i]$ 6: **end for** 7: Return(Q).

In order to optimize this algorithm, the succeeding point addition and doubling can be merged into a single function that calculates both results at the same time.

### 5.4 Comparison of Point Multiplication Algorithms

Because of the long runtime of point multiplication algorithms, a lot of research has been done in optimizing their performance. This overview assumes that  $char(K) \neq 2,3$ . So the Weierstrass equation can be written as  $E \setminus K$ :  $y^2 = x^3 + ax + b$ . The presented optimizations can be also applied to different underlying fields.

Affine method This is a straightforward implementation of the previously shown formulas. The problem with this implementation is the inverse. Calculating an inverse is computationally much more complex than multiplying or adding two values. Because of the resulting, excruciating runtime, it should not be considered for implementation.

- **Standard projection** The inverse of the affine method can be avoided by introducing a third coordinate. The point P = (x, y) can be transformed<sup>1</sup> to P = (X, Y, Z) where (x, y) = (X/Z, Y/Z). Firstly, this changes the elliptic curve equation to  $Y^2Z = X^3 + aXZ^2 + bZ$ . Secondly the addition and doubling formulas need to be changed.

- **Jacobian projection** Similar to the standard projection, a Jacobian projection can be used for transformation. In this case the point P can be represented as P = (X, Y, Z).  $P = (x, y) = (X/Z^2, Y/Z^3)$ . The new Weierstrass equation is  $Y^2 = X^3 + aXZ^3 + bZ^6$ . The resulting formulas for *point doubling*  $P_3 = 2P_1$  are:

$$X_3 = (3X_1^2 + aZ_1^4)^2 - 8X_1Y_1^2$$

(5.7)

$$Y_3 = (3X_1^2 + aZ_1^4)(4X_1Y_1^2 - X_3) - 8Y_1^4$$

(5.8)

$$Z_3 = 2Y_1 Z_1 \tag{5.9}$$

The resulting formulas for a *point addition*  $P_3 = P_1 + P_2$  are:

$$X_3 = (Y_2 Z_1^3 - Y_1)^2 - (X_2 Z_1^2 - X_1)^2 (X_1 + X_2 Z_1^2)$$

(5.10)

$$Y_3 = (Y_2 Z_1^3 - Y_1)(X_1 (X_2 Z_1^2 - X_1)^2 - X_3) - Y_1 (X_2 Z_1^2 - X_1)^3$$

(5.11)

$$Z_3 = (X_2 Z_1^2 - X_1) Z_1 \tag{5.12}$$

- **Double-and-add Algorithm** A lot of computation can be avoided by combining the *point addition* and *point doubling* algorithms. Parts of the formulas do not need to be calculated twice any more. This is specially advantageous in Algorithm 7 in which two points are always added and one of them is always doubled.

- **Montgomery ladder** The Montgomery ladder provides a very special optimization. The key is to keep the difference  $Q_1 Q_0$  constant. Algorithm 7 fulfills this property. Let us look at the example  $10100011_b \cdot P$  in table 5.1.

| bit | formula            |               | $Q_0$ | $Q_1$ | $Q_1 - Q_0$ |

|-----|--------------------|---------------|-------|-------|-------------|

| 1   | initializa         | tion          | P     | 2P    | Р           |

| 0   | $Q_1' = Q_0 + Q_1$ | $Q_0' = 2Q_0$ | 2P    | 3P    | P           |

| 1   | $Q_0' = Q_1 + Q_0$ | $Q_1' = 2Q_1$ | 5P    | 6P    | P           |

| 0   | $Q_1' = Q_0 + Q_1$ | $Q_0' = 2Q_0$ | 10P   | 11P   | P           |

| 0   | $Q_1' = Q_0 + Q_1$ | $Q_0' = 2Q_0$ | 20P   | 21P   | P           |

| 0   | $Q_1' = Q_0 + Q_1$ | $Q_0' = 2Q_0$ | 40P   | 41P   | P           |

| 1   | $Q_0' = Q_1 + Q_0$ | $Q_1' = 2Q_1$ | 81P   | 82P   | P           |

| 1   | $Q_0' = Q_1 + Q_0$ | $Q_1' = 2Q_1$ | 163P  | 164P  | P           |

Table 5.1: Point multiplication  $10100011_b \cdot P$  using Algorithm 7. The result is stored in  $Q_0$ .

$<sup>^{1}</sup>$ Lower case letters are used for normal coordinates. Upper case letters are used for projected coordinates.

Izu, Möeller and Takagi [21] presented a Montgomery Ladder. Their formulas already have another improvement built in. They are in a X-only point representation (see next item in this enumeration). The following part is taken from their paper.

Let  $x_1, x_2$  be x-coordinate values of two points  $P_1, P_2$  of an elliptic curve  $E: y^2 = x^3 + ax + b$ . Then the x-coordinate value  $x_3$  of the sum  $P_3 = P_1 + P_2$  is given by

$$x_3 = \frac{2(x_1 + x_2)(x_1x_2 + a) + 4b}{(x_1 - x_2)^2} - x'_3$$

(5.13)

where  $x'_3$  is the x-coordinate value of  $P'_3 = P_1 - P_2$ . On the other hand, the xcoordinate value of  $x_4$  of the doubled point  $P_4 = 2P_1$  is given by

$$x_4 = \frac{(x_1^2 - a)^2 - 8bx_1}{4(x_1^3 + ax_1 + b)}.$$

(5.14)

**X-only point representation** An optimization in connection with the Montgomery ladder is to avoid the calculation of the Y-coordinate. Consequently, memory and field operations can be saved. After the last operation the x-coordinates of  $kP = (x_1, y_1)$  and  $(k + 1)P = (x_2, y_2)$  have been calculated. If needed, the y-coordinate can be recovered using kP and (k + 1)P. Izu et al. also presented a formula for y-recovery, where  $Q_1 = (x_1, y_1), Q_2 = (x_2, y_2)$  and  $P = Q_2 - Q_1 = (x, y)$ .

$$y_1 = \frac{y^2 + x_1^3 + ax_1 + b - (x - x_1)^2(x_1 + x_2 + x)}{2y}$$

(5.15)

Using the previously introduced point projection, this formula works without an inversion.

**Common-Z point representation** Another optimization is to merge the z-coordinate of the two points used in algorithm 7. The points  $Q_1 = (X_1, Y_1, Z_1)$  and  $Q_2 = (X_2, Y_2, Z_2)$  can be represented as  $Q_1 = (X'_1, Y'_1, Z') = (X_1Z_2, Y_1Z_2, Z_1Z_2)$  and  $Q_2 = (X'_2, Y'_2, Z') = (X_2Z_1, Y_2Z_1, Z_2Z_1)$ .  $Z' = Z_1 \cdot Z_2$ . Consequently a register can be saved.

Different point multiplication methods are summed up in table 5.2. No distinctions are made between field multiplication and squaring algorithms. Usually a field squaring can be performed faster than a field multiplication. This is not the case for the implementation used in this thesis. Also the field addition and subtraction algorithms are accumulated.

It is possible to create double-and-add implementations for the *affine*, *standard projective and Jacobian projective* methods. They are not shown in this table. The last three implementations make use of Montgomery ladders. The last two implementations make use of a common-Z point representation.

The algorithm by Izu et al. actually needs 7 registers. The problem is that during multiplications, source registers are used as destination registers (e.g.  $A = A \cdot B$ ). For this operation, an extra register is needed as temporary storage.

An in-place field multiplication method does not support  $A = A \cdot B$ . The double and add algorithm by Auer does not use such multiplications. That is why hardly any extra memory is required. The cost of the memory reduction comes with the price of extra computation requirement.

| Method              | Reference | Registers | Calculation |

|---------------------|-----------|-----------|-------------|

| Affine Add          | [12]      |           | 1I + 3M     |

| Affine Double       | [12]      |           | 1I + 4M     |

|                     |           |           | 2I + 7M     |

| Std. Projective Add | [12]      |           | 14M         |

#### CHAPTER 5. ELLIPTIC CURVE CRYPTOGRAPHY

Std. Projective Double

Jacobian Add

Auer this work

Jacobian Double

Izu, Möller, Takagi

Table 5.2: Different multiplication Methods compared. 'I' is an inversion. 'M' is a multiplication. 'A' is an addition.

[12]

[12]

[12]

[21]

[4]

see App. D

$\frac{10M}{24M}$

16M

$\frac{8M}{24M}$

15M + 23A

18M + 22A

15M + 17A

$\frac{10}{7+1}$

7

8

The author tried to minimize the number of multiplications required by Auer's implementation. The resulting solution uses as many multiplications as Izu et al. An advantage is the minimized number of required additions. The source and destination registers of the multiplications are kept separately.

Because of the memory advantage of Auer's implementation, his algorithm has been used for all subsequent performance evaluations.

# Chapter 6

### **Prime Field Arithmetic**

This chapter provides algorithms to deal with prime fields  $\mathbb{F}_p$ . This is a special kind of field because it is finite. A finite field is also called Galois field.

A field can be seen as a set of elements with some properties. The two most important operations that can be used on a field are an addition and a multiplication. Other operations like a subtraction and a division can be derived from those operations. Very popular fields are the real field  $\mathbb{R}$ , the complex field  $\mathbb{C}$  or the field of rational numbers  $\mathbb{Q}$ . Those fields are not finite because they define an infinite set of numbers.

For each prime p, there exists a prime fields  $\mathbb{F}_p$  with p elements. Integer arithmetic modulo p forms such a prime field  $\mathbb{F}_p$ . An advantage is that an integer  $i \in \mathbb{F}_p$  can be represented with a fixed number of bits because  $\mathbb{F}_p$  contains a fixed number of elements. Prime fields are also well suited for cryptographic algorithms such as the ECDSA.

Because prime-field arithmetic is required for the elliptic curve digital signature algorithm it is described in this chapter. Or rather prime field arithmetic is described using an architecture with small word size W.

W usually is a multiple of 8 and is called a word. Because elements of  $\mathbb{F}_p$  usually are big integers, several words are needed to store such a big number.  $t = \lceil ld(p)/W \rceil$ words are needed to store an integer  $i \in \mathbb{F}_p$ . In the next sections, a and b are used to present such integers  $i \in [0, p - 1]$ . The memory cells used to store a can be written as  $(A[t-1], A[t-2], \dots, A[1], A[0])$ . The rightmost bit and word have the index zero. The index of the leftmost word is t - 1.

This chapter deals with the simpler addition, subtraction and multiplication operations. Those algorithms result into the majority of the runtime of the ECDSA algorithm. For the inversion (e.g. the Montgomery inversion) algorithm, the reader is encouraged to read the Chapter 2.2.5 in the Guide to Elliptic Curve Cryptography [12].

#### 6.1 Addition and Subtraction

The addition and subtraction algorithms usually are very fast and efficient. They are also a lot easier to implement than the multiplication algorithms, handled in Section 6.2.

One important thing to understand the Algorithm 8 is the carry propagation. When two W-wide words are added, the result has W + 1 bits. The extra, most significant bit is stored in the carry bit  $\varepsilon$ . The algorithm first adds a and b. If the sum is larger than or equal to p, p is subtracted from the intermediate result stored in c. In the case of the subtraction, performed within lines 6-9,  $\varepsilon$  is used as borrow bit.

**Algorithm 8** Prime field addition in  $\mathbb{F}_p$

**Require:** Two integers  $a, b \in [0, p-1]$  and a modulus p. **Ensure:**  $c = (a + b) \pmod{p}$ . 1:  $(\varepsilon, C[0]) \leftarrow A[0] + B[0].$ 2: for i from 1 to t - 1 do  $(\varepsilon, C[i]) \leftarrow A[i] + B[i] + \varepsilon.$ 3: 4: end for 5: if  $\varepsilon = 1$  or  $c \ge p$  then  $(\varepsilon, C[0]) \leftarrow C[0] - P[0].$ 6: for *i* from 1 to t - 1 do 7:  $(\varepsilon, C[i]) \leftarrow C[i] - P[i] - \varepsilon.$ 8: 9: end for 10: end if 11:  $\operatorname{Return}(c)$ .

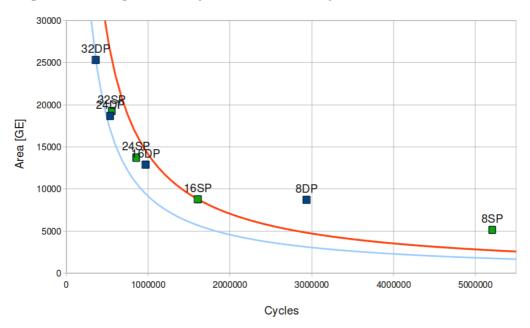

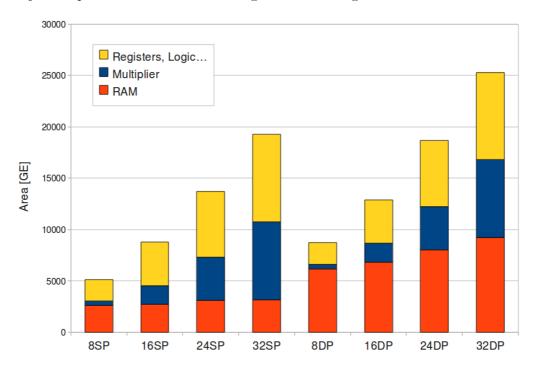

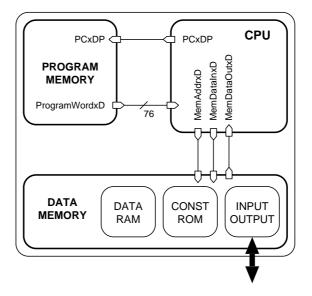

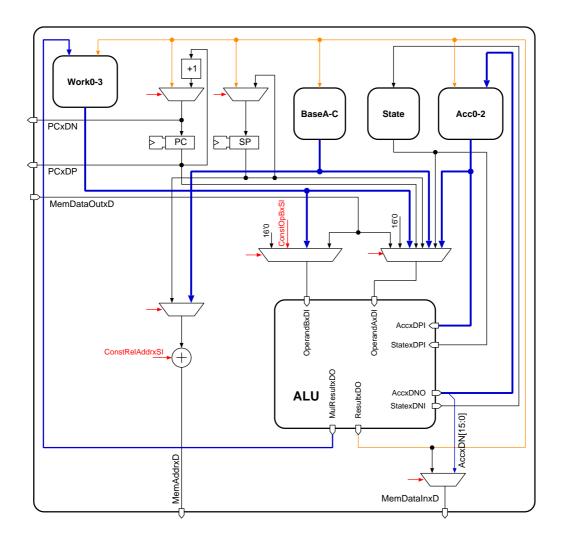

Algorithm 9 shows the subtraction procedure. It is very similar to the addition algorithm. A difference is in line 5. The extra check  $(c \ge p)$  is not required for a subtraction algorithm, because after the subtraction c = a - b, c cannot be larger than p. The algorithm first calculates the difference between a and b. If this difference is negative, p is added to the intermediate result stored in c.